2021-10-11

Practice Midterm Solution Thread.

Please post your solutions to your practice midterm problems to this thread.

Best,

Chris

Please post your solutions to your practice midterm problems to this thread.

Best,

Chris

Question 3

Partner: Chris Mccain

- Every identifier is declared before it is used

- No identifier is used in an inappropriate context

- Subroutine calls provide the correct number and types of arguments

- Any function with a non-valid return type returns a value explicitly

Question 3

Partner: Chris Mccain

# Every identifier is declared before it is used

# No identifier is used in an inappropriate context

# Subroutine calls provide the correct number and types of arguments

# Any function with a non-valid return type returns a value explicitly

Question 7 Nicholas Semaan, Yuanye Yang, Ameya Dighe There is 3 possibilities for 2 operators S + id | S - id | S * id Only id can also come. So, together it is given below Grammar S -> S|S + id S -> S|S - id S-> S|S * id S -> id(Edited: 2021-10-11)

<pre>

Question 7

Nicholas Semaan, Yuanye Yang, Ameya Dighe

There is 3 possibilities for 2 operators

S + id | S - id | S * id

Only id can also come.

So, together it is given below

Grammar

S -> S|S + id

S -> S|S - id

S-> S|S * id

S -> id

</pre>

Question 1 Andre Domingo, Mark Masulis a. Functional programming languages are based on lambda calculus. Functional programs use trees of expressions. Lisp is a functional programming language. b. A dataflow programming language uses functional nodes that activate upon receiving data. They can act in parallel. Verilog is a dataflow programming language. c. Logic-based programming languages define rules which the program follows. Programs run queries on these rules and receive an output. Prolog is a logic-based programming language. d. A von Neumann language alters program execution by changing values in memory. They are the most common programming languages. C is a von Neumann programming language.(Edited: 2021-10-11)

<pre>

Question 1

Andre Domingo, Mark Masulis

a. Functional programming languages are based on lambda calculus.

Functional programs use trees of expressions.

Lisp is a functional programming language.

b. A dataflow programming language uses functional nodes that activate upon receiving data.

They can act in parallel.

Verilog is a dataflow programming language.

c. Logic-based programming languages define rules which the program follows.

Programs run queries on these rules and receive an output.

Prolog is a logic-based programming language.

d. A von Neumann language alters program execution by changing values in memory.

They are the most common programming languages.

C is a von Neumann programming language.

</pre>

Jason Hammar Leo Alciso Edward Phan Question 2: Short answer: (a) If your C program consists of only one file, why may a linker still be used? (b) How is the loader for a compiled C program typically invoked (either *nix or Windows)? (c) What is a self-hosting compiler? (d) How does compiler bootstrapping work for self-hosting compilers?

Answer to (a): It is important to have a linker in a C program with one file because there may still be some object files you may need to link in an executable. An example would printf(); It can only be used with stdio.h.

Answer to (b): After the executable is made use ./ to load the program into ram and execute the main.

Answer to (c): A self-hosting compiler is a compiler that can compile its own source code.

Answer to (d): Bootstrap compiler is used to compile the compiler and then you can use this compiled compiler to compile everything else as well as future versions of itself.(Edited: 2021-10-11)

Jason Hammar

Leo Alciso

Edward Phan

Question 2:

Short answer:

(a) If your C program consists of only one file, why may a linker still be used?

(b) How is the loader for a compiled C program typically invoked (either *nix or Windows)?

(c) What is a self-hosting compiler?

(d) How does compiler bootstrapping work for self-hosting compilers?

Answer to (a): It is important to have a linker in a C program with one file because there may still be some object files you may need to link in an executable. An example would printf(); It can only be used with stdio.h.

Answer to (b): After the executable is made use ./ to load the program into ram and execute the main.

Answer to (c): A self-hosting compiler is a compiler that can compile its own source code.

Answer to (d): Bootstrap compiler is used to compile the compiler and then you can use this compiled compiler to compile everything else as well as future versions of itself.

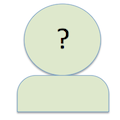

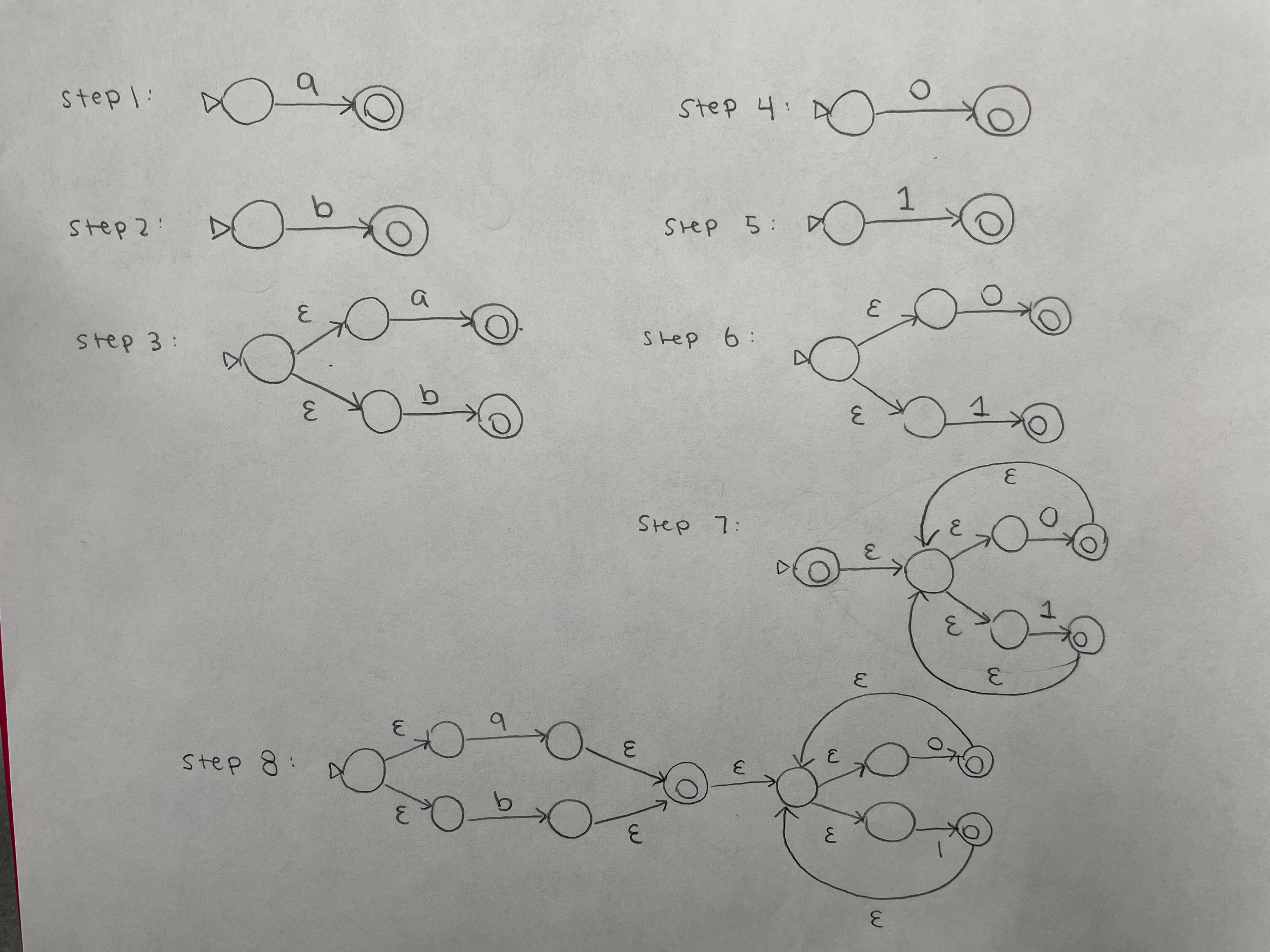

Christina Ng, Bill Li, Harrison Hwang

6. Show step-by-step how our procedure from class would convert the regular express (a|b)(0|1)* to an NFA.

(Edited: 2021-10-11) Christina Ng, Bill Li, Harrison Hwang

6. Show step-by-step how our procedure from class would convert the regular express (a|b)(0|1)* to an NFA.

((resource:244998104_451888649589806_771300088713063495_n.jpg|Resource Description for 244998104_451888649589806_771300088713063495_n.jpg))

Q4:

Connor Pietrasik, Thanh Le, Brandon Ong

(Edited: 2021-10-11)

include <stdio.h>

include <math.h>

typedef struct Polar{

float angle;

float r;

} Polar;

int main(void){

FILE* fp = fopen("foo.txt", "r");

//Figured having a max amount is fine since it's a test and we'll be rushing

Polar coords[20];

int count = 0;

float x, y;

for (; fscanf(fp, "%f,%f", &x, &y) > 0; count++){

coords[count].r = sqrt(x * x + y * y);

coords[count].angle = atan(y / x);

}

for (int i = 0; i < count; i++){

printf("%.2f\n", coords[i].angle);

}

return 0;

}

Q4:

Connor Pietrasik, Thanh Le, Brandon Ong

<pre>

#include <stdio.h>

#include <math.h>

typedef struct Polar{

float angle;

float r;

} Polar;

int main(void){

FILE* fp = fopen("foo.txt", "r");

//Figured having a max amount is fine since it's a test and we'll be rushing

Polar coords[20];

int count = 0;

float x, y;

for (; fscanf(fp, "%f,%f", &x, &y) > 0; count++){

coords[count].r = sqrt(x * x + y * y);

coords[count].angle = atan(y / x);

}

for (int i = 0; i < count; i++){

printf("%.2f\n", coords[i].angle);

}

return 0;

}

</pre>

Ian Chavez

Jesse Dong

Question 9:

Define the following concepts related to stack and heap based allocation:

Frame Pointer - Value pointing to the base address of the called

function’s instance frame. Used because stack frame location

cannot be predicted at compile time.

Calling Sequence - The set of instructions to set up and call a subroutine,

as well as get the required data for the subroutine, as well

as tell the computer where to return after the subroutine is executed.

Buddy System Heaps - Method of splitting memory based on best fit,

if 2^k is too small, find a 2^k+1 size block, divide by 2 and

check if it fits. If it fits, put spare half to the free list.

Once used half is deallocated, combine with the spare half.

Garbage Collection - Process that runs on a continuous thread

that periodically wakes up to check for memory that do not

have a reference pointer.

(Edited: 2021-10-11) Ian Chavez

Jesse Dong

Question 9:

Define the following concepts related to stack and heap based allocation:

Frame Pointer - Value pointing to the base address of the called

function’s instance frame. Used because stack frame location

cannot be predicted at compile time.

Calling Sequence - The set of instructions to set up and call a subroutine,

as well as get the required data for the subroutine, as well

as tell the computer where to return after the subroutine is executed.

Buddy System Heaps - Method of splitting memory based on best fit,

if 2^k is too small, find a 2^k+1 size block, divide by 2 and

check if it fits. If it fits, put spare half to the free list.

Once used half is deallocated, combine with the spare half.

Garbage Collection - Process that runs on a continuous thread

that periodically wakes up to check for memory that do not

have a reference pointer.

Question 5: Daniel Pu and Andy Luong

Makefile is a build utility that defines a set of tasks to be executed on certain

files. They are also a simple way to organize code compilation as you can simply

type ‘make “task name”’ in the console within the correct directory, which will

execute the commands corresponding to the task for you.

Variables are names in the Makefile that represent a string(s) of text, which is

also known as the variable’s value. These variables along with their values can be

substituted within the rest of the Makefile as requests to targets, dependencies,

or commands. To use variables in make files, type a dollar sign with parentheses

or braces and in it is the variable name like $(objects). For notations, $@ refers

to the name of the target that is being generated, $< refers to the first

prerequisite of the target, and $^ refers to all prerequisites for the target.

An example program with more than one target and with a clean target in C can be the following:

objects = program.o foo.o utils.o

program : $(objects)

cc -o program $(objects)

$(objects) : defs.h

all: output main.o message.o

output: main.o message.o

gcc main.o message.o -o output

main.o: main.c

gcc -c main.c

message.o: message.c message.h

gcc -c message.c

clean:

rm -rf output

(Edited: 2021-10-11) <nowiki>Question 5: Daniel Pu and Andy Luong

Makefile is a build utility that defines a set of tasks to be executed on certain

files. They are also a simple way to organize code compilation as you can simply

type ‘make “task name”’ in the console within the correct directory, which will

execute the commands corresponding to the task for you.

Variables are names in the Makefile that represent a string(s) of text, which is

also known as the variable’s value. These variables along with their values can be

substituted within the rest of the Makefile as requests to targets, dependencies,

or commands. To use variables in make files, type a dollar sign with parentheses

or braces and in it is the variable name like $(objects). For notations, $@ refers

to the name of the target that is being generated, $< refers to the first

prerequisite of the target, and $^ refers to all prerequisites for the target.

An example program with more than one target and with a clean target in C can be the following:

objects = program.o foo.o utils.o

program : $(objects)

cc -o program $(objects)

$(objects) : defs.h

all: output main.o message.o

output: main.o message.o

gcc main.o message.o -o output

main.o: main.c

gcc -c main.c

message.o: message.c message.h

gcc -c message.c

clean:

rm -rf output

</nowiki>

(c) 2024 Yioop - PHP Search Engine